- 打卡等级:初来乍到

- 打卡总天数:9

- 最近打卡:2026-03-20 16:42:01

中级会员

- 积分

- 413

|

发现stc32g144k-256的DMA-DAC输出间隔有一个固有延时,不知道是什么原因。

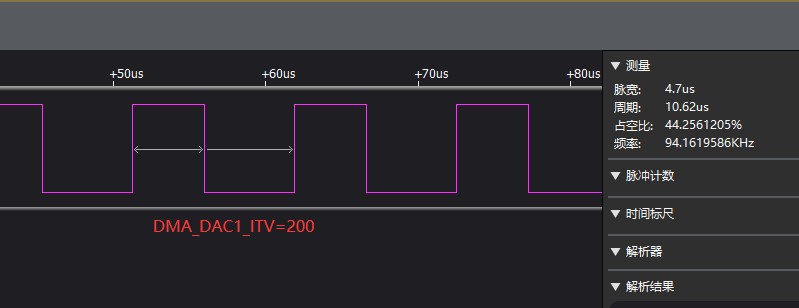

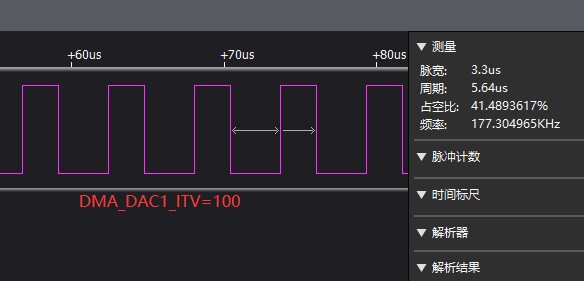

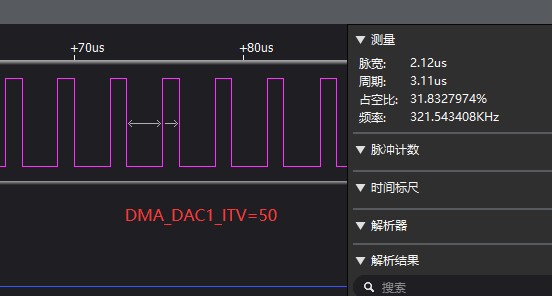

以40M主频,用MDA-DAC交替输出0和4095, 用逻辑分析仪捕捉其输出间隔

按理论计算当ITV设置50,100,200时,其输出间隔应该是1.25us, 2.5us, 5us.

但实际输出间隔约为1.55us, 2.8us, 5.3us,都比理论计算要高约0.3us。

忽略各种误差的情况下,可以得出结论:输出间隔比理论计算要高出约12个系统周期。

改变主频,上面论结论依然成立。

测试代码如下

#include "stc32g144k.h"

typedef unsigned short u16;

typedef unsigned char u8;

u16 xdata buf[200] = {

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f, 0x0000, 0xff0f,

};

//40M主频

void main()

{

EAXFR = 1; //扩展寄存器(XFR)访问使能

WTST = 1;

CKCON = 0; //提高访问XRAM速度

P0M0 = 0;

P0M1 = 0X21; // P00 P05设置高阻

PGA1_CR1 = 0X53;// 缓冲模式 PGA1正极端口选择DAC1O PGA1 负极端口选择P05 PGA1输出端口选择P00、

PGA1_CR2 = 0X04;

DMA_ARB_CFG = 0x00;//切换到xdata部分

DMA_DAC1_TXAH = (u8)((u16)buf >> 8); //地坛

DMA_DAC1_TXAL = (u8)((u16)buf);

DMA_DAC1_ITVH = 0; //间隔

DMA_DAC1_ITVL = 50; //25ns * 50 = 1.25us

//DMA_DAC1_ITVL = 100; //25ns * 100 = 2.5us

//DMA_DAC1_ITVL = 200; //25ns * 200 = 5.0us

DMA_DAC1_AMTH = 0; //传输数量

DMA_DAC1_AMT = 99;

DMA_DAC1_CFG = 0X03; //数量总线最优先级。

DAC1_DIV = 0;

DAC1_CR = 0XB1;

DMA_DAC1_CR = 0XC0; //使能并触发

while(1)

{

if (DMA_DAC1_STA & 0X01)

{

DMA_DAC1_CR = 0XC0; //使能并触发

DMA_DAC1_STA = 0;

}

NOP4();

}

}

dma-dac-test.rar

(61.19 KB, 下载次数: 0)

dma-dac-test.rar

(61.19 KB, 下载次数: 0)

|

|

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )